# New technique for quadrilateral distance relay

V. T. Ingole, B.E., M. Tech., M. T. Sant, B.E., M. Tech., and Y. G. Paffhankar, M.E., Ph.D.

Indexing terms: Monitoring, Power-transmission lines, Relay protection

### ABSTRACT

A new technique for the development of a quadrilateral distance relay for transmission-line protection is reported. The modus operandi consists in continuously monitoring the coincidence period of four suitably derived relaying quantities, and the relay is made to develop trip output if the coincidence period is zero, whereas if the coincidence period is finite, the relay develops restraining output. Such a simple criterion, results in extreme simplicity of the relay circuitry.

#### LIST OF SYMBOLS

#### 1 INTRODUCTION

The rapid growth of power systems owing to increasing demand, as well as interconnections, has resulted in e.h.v. Imes being used over longer distances to deliver the bulk of the power. However, such long and heavily loaded lines demand that greater attention be paid to the problems arising out of the encroachment of the loci of maximum load and power swings into the distance-relay characteristic. Attempts to overcome these problems have resulted in the quadrilateral characteristic, which fits the fault characteristic of the transmission line tairly well.

Although numerous techniques 0-70 have been reported for developing such a characteristic, most of them either require larger numbers of relaying inputs and/or quite an elaborate circuit. The new technique that is reported here required four relaying inputs and an extremely simple circuit.

### 2 SUGGESTED TECHNIQUE

### 2.1 Relaying quantities

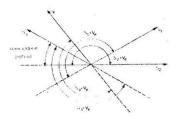

The desired quadrilateral characteristic, defined by the extremities of phasors  $Z_{\bf q}, Z_{\bf b}$  and  $Z_{\bf c}$ , is shown in Fig. 1A, whereas Fig.1B shows the relaying quantities for any relay impedance phasor  $Z_{\bf r}$ , defined by point  $P_{\bf l}$ .

Fig 1A

Quawiluteral polar characteristic

Paper 7158 P, first received 31st October 1973 and in received form 12th February 1974

Mr. V. T. Ingole is with the R & D Department of Crompton Greave, Worli, Bombay, India, and Mr. M. T. Sord and Dr. Y. G. Paithankar are with the Viscosvaraya Regional College of Engineering, Nagpor 440011, India The relaying quantities are thus defined as

$$\begin{split} & \Sigma_{1} - Z_{\alpha} - Z_{\Gamma} - 1_{\Gamma}, Z_{\Omega} - V_{\Gamma} \\ & S_{2} + Z_{D} - Z_{\Gamma} - 1_{\Gamma}, Z_{D} - V_{\Gamma} \\ & S_{3} + Z_{C} - Z_{\Gamma} + 1_{\Gamma}, Z_{C} - V_{\Gamma} \\ & S_{4} - - Z_{\Gamma} + - V_{\Gamma} \end{split}$$

Fig. 1B

Relaying quantities

# 2.2 Properties of relaying inputs in trip and restraining region

in Fig. 1B, the relay impedance phasor  $Z_r$ , defined by point  $\Gamma_1$ , is shown in the restraining region. Observing the phasor dispositions of the relaying quantities  $S_1$  to  $S_4$ , the following general conclusion is drawn:

Whenever the relay impedance phasor  $Z_{\rm F}$  is in the restraining region, all the relaying phasors are confined to 180° phase-angle margin.

Fig. 2 shows the relay impedance phasor  $Z_{\rm P}$ , defined by point  $P_2$  as crossed over into the trip region. The conclusion relating to the phasor dispositions of relaying quantities  $S_1$ - $S_4$  is now found to be:

Fig. 2 Phasor dispositions of  $S_4$ - $S_4$  for  $Z_7$ in trip region

PROC. 1EE, Vol. 121, No. 6, JUNE 1974

'Whenever the relay impedance phasor  $Z_r$  is in the trip region, all the relaying phasors are confined to more than  $180^\circ$  phase-angle margin'

# 2.3 Coincidence periods of relay inputs in restraining and trip region

Figs. 3A and B show, respectively, the relay phasor positions as confined to 180° phase-angle margin (for  $\rm Z_r$  in restraining region), and confined to more than 180° phase-angle margin (for  $\rm Z_r$  in trip region). The conclusions with regard to their coincidence period are as follows:

- (a) In the restraining region, the coincidence period is finite and is governed by two extreme phasors.

- finite and is governed by two extreme phasors.

(b) In the tripping region, the coincidence period is zero or there is no coincidence period.

Fig. 3A

Finite coincidence period for phasors confined to less than 180° phase-angle margin

Fig. 3B Zero coincidence period for phasors confined to more than 180° phase-angle margin

## 2.4 Principle and block diagram of relay

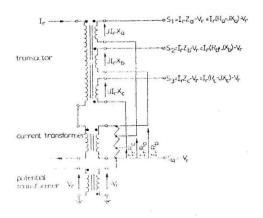

Fig. 4 shows the complete block diagram of the relay

The relaying inputs  $\mathbf{S_1}\text{-}\mathbf{S_4}$  are derived as functions of  $\mathbf{V_p}$  and  $\mathbf{I_p}$ , with the help of replica impedances  $\mathbf{Z_a}, \mathbf{Z_b}$  and  $\mathbf{Z_c}$  and a potential transformer.

These inputs are then fed to a coincidence gate, which delivers output pulses periodically, every 20 ms, based on a power frequency of 50 Hz, for  $Z_\Gamma$  in the restraining region. The pulse stretcher, which is a 20 ms monostable frigg, ring on the leading edge of the input pulses, delivers continuous output to energise a slave relay having normally closed contacts. The contacts are thus kept open for  $Z_\Gamma$  in the restraining region.

Whenever  $\mathbf{Z}_{\mathbf{r}}$  falls in the tripping region owing to fault conditions on the line, the coincidence gate, and thus the pulse stretcher, delivers no output, resulting in the drop out of the slave relay. The slave relay, therefore, closes its contact as in indication of trip output.

### 3 PROTOTYPE RELAY

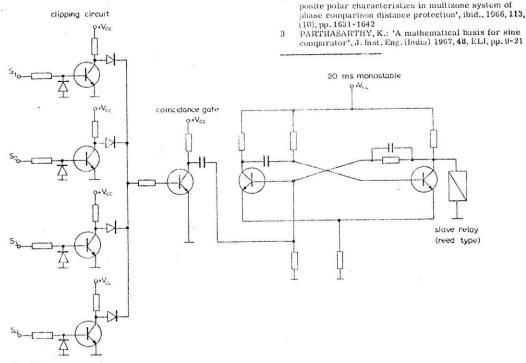

The circuit arrangement of the relay unit based on the above principle is shown in Fig. 5.

Fig. 5A Derivation of relacing inputs

Fig. 5A shows how the four relaying inputs  $\mathbf{S}_1$ – $\mathbf{S}_4$ , as functions of  $\mathbf{V}_r$  and  $\mathbf{I}_p$ , are derived with the help of a transactor, an auxiliary current transformer and an auxiliary potential transformer, whereas Fig. 5B shows the transistor circuitry consisting of four clippers, a NAND gate, a monostable as a 20 ms pulse stretcher and the slave relay (reed type).

### 4 EXPERIMENTAL RESULTS

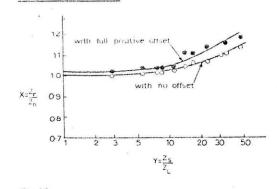

The static polar characteristic is shown in Fig. 6A, for a constant value of  $I_{\rm T}$  equal to 1.0 A.

Accuracy/range characteristics for steady-state and fully offsed conditions of the relay current are shown in Fig. 6. The relay operated within an accuracy of  $10^\circ$ L up to a range of 30, and the maximum transient overreach was found to be  $7^\circ$ L.

The operating time was found to vary from instantaneous to a maximum of one cycle (20 ms) depending on the instant of fault.

The burden of potential circuit and the current circuit was found to be 0.4 VA and 0.5 VA, respectively.

### 5 CONCLUSIONS

A novel technique has been presented for developing a quadrilateral distance relay, requiring four suitably derived

Fig. 4

Block diagram of relay

PROC. IEE, Vol. 121, No. 6, JUNE 1974

relaying inputs, followed by a very simple circuitry, the modus operandi of the relay being the generation of trip outand if the coincidence period of the four relaying quantities is zero.

Fig. 5B Relay circuitry

Static polar characteristic at constant  $I_r = 1.0 A$

The experimental results show quite satisfactory performance with respect to the operating range, transient over-reach, VA burden and the operating time, except that the relay, in the present form, tends to maloperate when not energised, i.e. in the absence of basic relaying inputs  $I_{\rm p}$  and  $V_{\rm p}.$  This difficulty is being overcome by providing a suitable bias to the slave relay, derived from the output of a NAND gate, supplied with the rectified (tuilwaye) relay inputs  $\mathbf{I}_r$  and  $\mathbf{V}_r$ . This arrangement further ensures the correct directional feature for the relay by positively excluding the origin of the R/X diagram from the trip region of the relay.

Fig. 6B Accuracy versus range characteristics

REFERENCES

HUMPAGE, W.D., and SABBERWAL, S. P.: 'Develop-

ments in phase comparison techniques for distance protection', Proc. IEE, 1965, 112, (7), pp. 1383-1395

HEL, H., MARSHALL, G., and CHAPMAN, C. P.: 'Com-

6.

- PARTHASARTHY, K.: 'A three step transistorised distance relay with a quadrilateral distance character-

- istic, J. Inst. Eng. (India) Electr, Eng. Div., 1967, 2, pp. 189-204

KINCHA, H. P., PARTHASARTHY, K., and ASBOK

KUMAR.: 'Developments in amplitude comparator technique for distance relays', Proc. IEE, 1970, 117,

- (6), pp. 1118-1124

ANIL KUMAR, N. M.: 'New approach to distance relays with quadrilateral polar characteristic for e.h.v. line protection', ibid., 1970, 117, (16), pp. 1986-1992

KINCHA, H. P., PARTHASARTHY, K., ASHOK KUMAR

- and ARUN, C.G.: 'New possibilities in amplitude and phase-comparison rechniques for distance relays', ibid., 1970, 117, (11), pp. 2133-2141